## How to upgrade XO memory from 256 MB to 512 MB

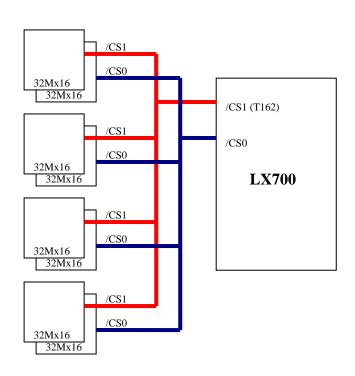

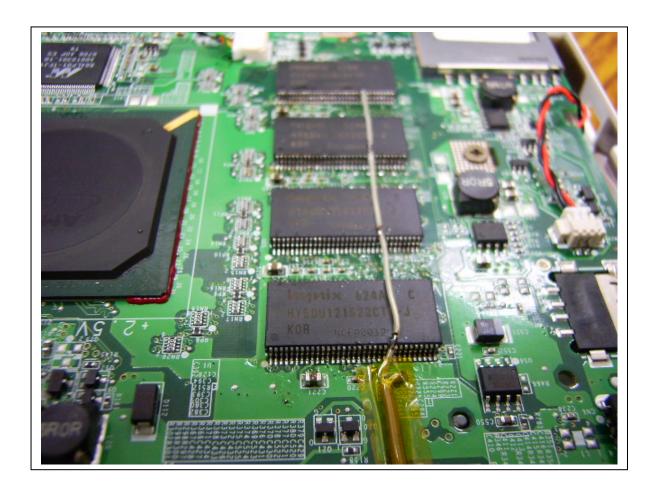

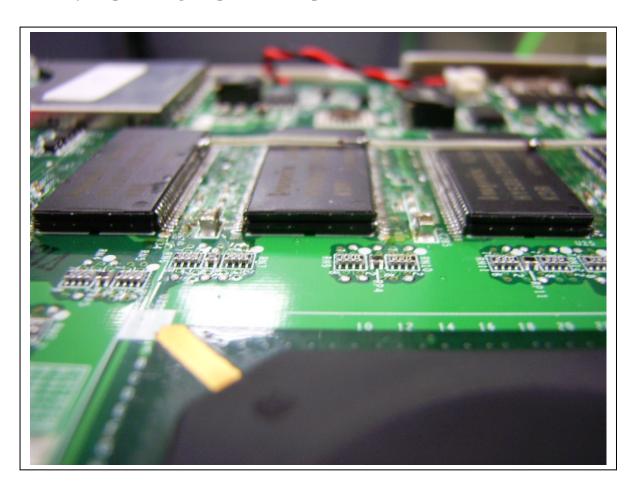

XO Current memory configuration was 32Mb x 16 x 4 = 256MByte Soldering extra four 32MbX16 memory component on top of original memory component the /CS Chip select (pin 24) must connect to test point T162 (CPU memory controller /CS1)

| <u>x4</u>                                                                                                                                                                                                                              | <u>x8</u>                                                                                                                    | <u>x16</u>                                                                                                             | _                                                                                              |                                                                      |                                                                                                                                                                                                                            | <u>x16</u>                                                                                                            | <u>x8</u>                                                                                                           | <u>x4</u>                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| VDD<br>NC<br>VDDQ<br>NC<br>DQ0<br>VSSQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>VDDQ<br>NC<br>VDD<br>NC<br>NC<br>VDD<br>NC<br>NC<br>NC<br>VDDQ<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC | VDD DQ0 VDDQ NC DQ1 VSSQ NC DQ2 VDDQ NC DQ3 VSSQ NC NC VDDQ NC NC VDDQ NC NC NC NC NC AC | VDD DQ0 VDDQ DQ1 DQ2 VSSQ DQ3 DQ4 VDDQ CSSQ DQ7 NC VDDQ LDQS NC LDM WE /CAS /CAS /RAS /RAS /RAS /RAS /RAS /RAS /RAS /R | 1 2 3 4 5 6 6 7 8 9 10 11 12 13 14 15 16 16 16 16 17 18 19 19 19 19 19 19 19 19 19 19 19 19 19 | 400mil X 875mil<br>66pin TSOP -II<br>0.65mm pin pitch<br>(Lead free) | 66<br>64<br>63<br>64<br>63<br>61<br>60<br>59<br>58<br>57<br>55<br>54<br>49<br>48<br>47<br>46<br>44<br>43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36 | VSS DQ16 VSSQ DQ11 VSSQ DQ11 VSSQ DQ10 DQ9 VDDQ VDDQ VSSQ UDQS NC VSSQ UDQS NC CK | VSS DQ7 VSSQ NC DQ6 VDDQ NC DQ5 VSSQ NC DQ4 VDDQ NC VSSQ DQS NC VREF VSS DM /CK CK CKE NC A11 A9 A8 A7 A6 A5 A4 VSS | VSS NC VSSQ DQS NC VREF VSS DM DM A8 A7 A6 A5 A4 VSS |

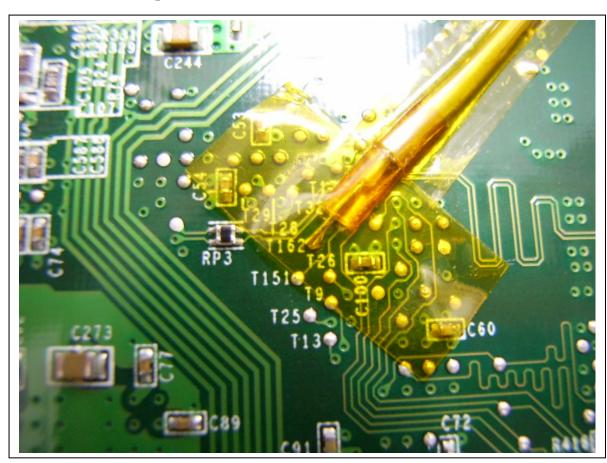

Use Coaxial cable and shelling GND will increase signal quality. ( Memory Chip select signal speed almost up to 100 Mhz )

/CS1 connect to Test point T162 on circle board back side.

```

acue ruante.

Luablea

Cache Mode

LZ Cache Enable:

Enabled

Cache All

DIMM 0

DIMM 1

Memory Optimization DIMMO:

Manual

Memory Opt

DIMM 0 Page Size:

8 KB

DIMM 0 Size:

512 MB

Number of Devices:

8 devices

DIMM 0 Module Banks:

2 banks

DIMM 0 Component Banks: 4 banks

CAS Latency:

Auto

Memory Laten

Refresh Rate: Auto

Interleave Select:

LOI

XOR BAO: Disabled

XOR BA1: Disabled

```

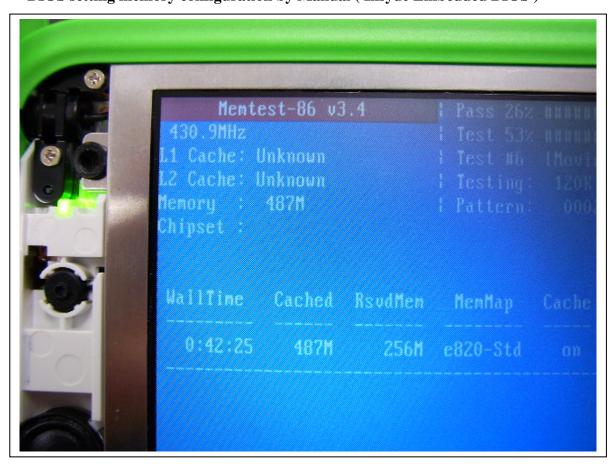

**BIOS** setting memory configuration by Manual (Insyde Embedded BIOS)

Running Memtest-86 V3.4 almost 200 hours without any Error.

This is very popular design on DDR1 DIMM module field for cost down purpose <a href="http://www.valueram.com/datasheets/KVR266X72RC25L\_2G.pdf">http://www.valueram.com/datasheets/KVR266X72RC25L\_2G.pdf</a>