Measure/Projects/Signal-Generator: Difference between revisions

(→Detailed circuit description: add circuit drawing) |

|||

| Line 14: | Line 14: | ||

== Detailed circuit description == |

== Detailed circuit description == |

||

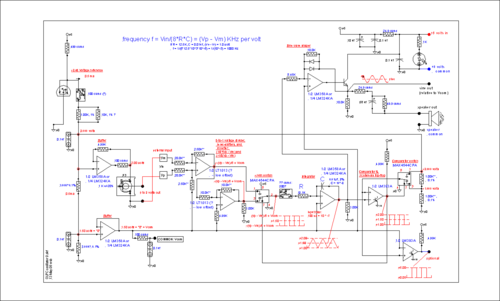

[[Image:OLPC oscillator 0.PNG|thumbnail|500px|right|An extremely rough "sketch" to give the idea. My inclination is to do away with the sine wave shaper and the "driver" circuit (the driver circuit creates enough disturbance on the "ground" line via "common impedance coupling" to bother the circuit. More to follow.]] |

|||

:(This will eventually be moved to the end). |

:(This will eventually be moved to the end). |

||

| Line 35: | Line 37: | ||

: '''Fcyc = Vin/(4*R*C*|Vthr|)''' |

: '''Fcyc = Vin/(4*R*C*|Vthr|)''' |

||

where Vin is the voltage R is the resistance in ohms, C is the capacitance in farads, and |Vthr| signifies the positive value of the upper- and lower threshold-voltages, Vu and VL, assumed equal. All voltage measurements in this formula are defined and measured relative to an artifical "zero" called Vcom. In +5 volt-only circuits, such an artifical zero must be defined to be at least 1 volt above the true circuit "0". |

where Vin is the voltage R is the resistance in ohms, C is the capacitance in farads, and |Vthr| signifies the positive value of the upper- and lower threshold-voltages, Vu and VL, assumed equal. All voltage measurements in this formula are defined and measured relative to an artifical "zero" called Vcom. In +5 volt-only circuits, such an artifical zero must be defined to be at least 1 volt above the true circuit "0". |

||

== Detailed circuit analysis == |

== Detailed circuit analysis == |

||

Revision as of 01:40, 24 May 2008

Purpose of a signal generator

A number of Measure activities require a "signal generator" -- a electronic device to create sine waves of known frequency in the audible range, i.e. rougly in the range of a piano keyboard (0 Hertz (cycles per second) to 2500 Hz.) Perhaps the laptop itself can be used this way too. But a goal of the design described here is to double as a "voltage-to-frequency converter" -- put in +1.000 volts and get out 1000 Hz, put in 0.440 volts and get out A-440, the international tuning pitch.

Specifications

- Frequency range -- 0 Hz to approximately 2500 Hz

- Frequency accuracy -- ideal is +/- 1 cycle, but unlikely. Calculations indicate +/-0.5% is possible in the range of 0 to 2000 Hz, i.e. +/-10 cycles at 2000 Hz with variations of power voltage 4.5 volts to 5.5 volts. Trim to +/-1 Hz at 1000 Hz and 1.000 volts input.

- Cost target -- under $10 US total parts cost in 100 piece quantity.

- External voltage input -- 0 to +5 volts relative to circuit ground. No harm should come to the circuit or laptop if the voltage is reversed.

- Output --

- Triangle wave: 1.00 volt peak-to-peak triangle wave (TBD -- goal is 2.00 volts peak-to-peak to improve accuracy but there are issues with the opamps) into a "homemade" speaker, symmetric to 1 part per thousand (the goal: actual TBD) around common voltage Vcom (actual signal peaks levels relative to Vcom may be +/-0.005 volts.)

- Sine wave: TBD. Derived from the triangle wave and shaped by diode limiters.

- Square wave: TBD. Derived from the triangle wave and shaped by a comparator.

- Vcom: "Common" or reference voltage for the triangle wave: 1.50 volts +/0.005 volts (TBD).

Detailed circuit description

- (This will eventually be moved to the end).

This circuit is uses some design concepts of the Measure/Projects/Oscilloscope probe, in particular the circuit's voltage reference derived from a TL431ACZ and the level-shifting and input protection achieved with a differential amplifier.

This oscillator falls in the general class of oscillators known as the hysteresis RC oscillator -- RC for Resistance-Capacitance, "hysteresis" for the fact that it derives its memory from feedback.

The design evolved from the intention to eke out the highest possible performance (accuracy) with the lowest cost and most readily-available parts. This [spec? deisre?] dictates a thorough analysis -- both design to determine the critical components and statistical to study variations.

A couple of common RC oscillator circuits exist: the 555 timer and the hysteresis oscillator. Both employ two thresholds or voltage-comparison points -- an upper threshold Vu and a lower threshold VL - and a memory. There are other possibilities for oscillators -- in particular the Colpitts oscillator, the quadrature oscillator, the phase-delay oscillator. None lend themselves to variable frequency generation.

I experimented with a number of RC versions:

- (1) traditional 555 timer (contains two voltage comparators and a flip-flop memory) -- discarded because the two voltage comparision points (the upper and lower thresholds) are not accurate enough in a given part, and they vary from unit to unit.

- (2) circuit similar to a 555 timer, i.e. built instead with two accurate voltage references (upper and lower thresholds accurage to 0.001 volt), 2 LM339A comparators (4 in a package) and a flip-flop built with the other two comparartors. Surprisingly, this circuit has too much transition delay (i) between actually sensing that the voltage from the integrator has hit a threshold, and (ii) actually propagating this information to the flip-flop. Various efforts to improve this failed.

- (3) Hysteresis flip-flop without use of analog switch: The LM393A or LM339A comparator has a distinct non-zero output caused by the saturated output transistor (either FET or a bipolar). This caused an error.

- (4) Hysteresis flip-flop with analog switch, voltage-fed: Derive the upper and lower threshold voltages from a resistor ladder fed and buffer these voltages with op amps. Feed these two voltages to an analog switch -- a Maxim MAX4544CPA Single-Pole-Double-Throw (SPDT) analog switch.

The basic formula for the output frequency Fcyc of the triangle wave -- but without any scaling or errors included -- is the following:

- Fcyc = Vin/(4*R*C*|Vthr|)

where Vin is the voltage R is the resistance in ohms, C is the capacitance in farads, and |Vthr| signifies the positive value of the upper- and lower threshold-voltages, Vu and VL, assumed equal. All voltage measurements in this formula are defined and measured relative to an artifical "zero" called Vcom. In +5 volt-only circuits, such an artifical zero must be defined to be at least 1 volt above the true circuit "0".

Detailed circuit analysis

- (This will eventually be moved to the end).

Locations of sensitivity in the circuit:

- 1 Voltage reference(s): 1 voltage reference TL431ACZ, 2 offsets, 2 resistors

- 2 Input voltage level-shifter and inversion circuit: (6 resistors, 2 offset voltages)

- 3 Integrator -- 1 resistor and 1 capacitor (trimmable)

- 4 Triangle comparator -- two resistors and 1 voltage reference (trimmable)

Single-supply circuits: A restriction to these types of circuits removes any risk of accidently inputting "strong" negative voltages into the laptop.

Artifical-Zero circuit -- circuit constraints: True +5 volt-only circuits such as the one we will use here require an artificial zero. Two significant constraints exist in such circuits:

- (1) No single-supply op amp can pull down its output to true 0. The typical ones begin to poop out noticeably at about +0.5 volts above 0. This becomes grevious (measureable, observable) when the output "load" (resistance) is more than about 10 microamps.

- Inexpensive op amps such as the LM324A or KA or LM358A show a significant degradation of output current when the output voltage is

- (2) Some op amps can (sort of) pull their outputs up to e.g. +5 volts, but can be assumed to (truly, actually) poop out at about Vpower - 1.5 volts:

- Example: On a good day, this means that when Vpower = 5.0 volts, that the maximum signal inside the circuit should not exceed +3.5 volts. on a bad day when Vpower = 4.5 volts, that means that the maximum signal inside the circuit should not exeed +3.0 volts. We'd like a bit of design margin in this too, so if we specify Vpower = +4.25 volts min, then 4.25 - 1.5 = 2.75 volts is the maximum usable signal-voltage anywhere in the circuit.

Circuit constraints caused by a power driver: If we include a "power driver" circuit to power a speaker, the circuit will require a transistor (probably an NPN 2N2222A or equivalent). This transistor has a Vbe of ~0.6 volts. The op amp that drives this transistor must be able to pull its output up +0.6 volts beyond the actual, desired output voltage. This further compresses our output by another 0.6 volts, or 2.75 - 0.6 or about down to 2.1 volts.

These two constraints severely limit our useable signal range to the following:

- 0.5 volts < Vcircuit-signals < 2.1 volts

In all the above cases, the design integrates current from an input voltage +/-Vin through R into capacitance C. That is, the voltage across the capacitor is caused by the electrical charge Q in the capacitor divided by its capacitance C: Vcap = Q/C. This change in charge Q1 - Q0 represents the accumulation (integral) of the current i (amperes per second) times the time duration (T1-T0) that the current is flowing into or out of capacitance C: (Q1-Q0) = i*(T1-T0). In this design, current i is forced into capacitor C at a known rate i.e. i = Vin/R. So these three equations:

- Vcap = Q/C; change in capacitor voltage (Vcap1 - Vcap) = (Q1 - Q0)/C

- Q = i*T; change in capactior charge (Q1 - Q0) = i*(T1 - T0)

- i = Vin/R, a constant

yield the change in capacitor voltage during the time interval (T1 - T0):

- (Vcap1 - Vcap0) = (Q1-Q0)/C = (i*(T1-T0))/C = ((Vin/R)*(T1-T0))/C = Vin*(T1-T0)/(R*C).

There are four intervals or "phases" during a cycle of charging and discharging between the upper threshold-voltage Vu and the lower threshold voltage VL. In this analysis the "0" or common voltage is assumed to be 0 volts. In reality it will be Vcom = +1.5 volts:

- (1) Capacitor C is discharged; voltage Vcap is 0: the integrator op amp pushes current into capacitor C and Vcap charges (increases) to Vu: (Vu - 0) = +Vin*(T1-T0)/(R*C)

- (2) Capacitor voltage starts at Vu, but now Vin changes sign to minus, the op amp sucks current out of capacitor C, and C discharges to Vcap = 0: (0 - Vu) = -Vin*(T2-T1)/(R*C)

- (3) Again the capacitor voltage Vcap starts at 0 but Vin is negative and the op amp continues to suck current from capacitor C: Vcap disharges to VL -- here we must remember that VL is negative with respect to 0: (VL - 0) = -Vin*(T3-T2)/(R*C)

- (4) Capactior voltage starts at VL (and VL is negative), but now Vin changes sign to plus, the op amp pushes current i into capacitor C, and it charges to Vcap = 0: (0 - VL) = +Vin*(T4-T3)/(R*C).

The total cycle time Tcyc is the time required for the voltage Vcap to start at 0, go to Vu, decrease to 0, decrease to VL, and increase back to 0 again. Thus

- Tcyc = T4 - T0 = (T4 - T3) + (T3 - T2) + (T2 - T1) + (T1 - T0)

- Tcyc = (0 - VL)*(R*C)/(+Vin) + (VL - 0)*(R*C)/(-Vin) + (0 - Vu)*(R*C)/(-Vin) + (Vu - 0)*(R*C)/(+Vin)

- Tcyc = (R*C)*[ ( 2*(-VL/Vin) + 2*(Vu/Vin) )

- Tcyc = (2*R*C)/Vin * (Vu - VL)

The "frequency" Fcyc of a cycle is the inverse of this:

- Fcyc = 1/Tcyc = Vin/(2*R*C*(Vu - VL))

If the upper and lower thresholds are of equal absolute value, e.g. Vu = 0.5 and VL = -0.5 so that |Vthr| = |Vu| = |VL| then we have the classical formula:

- Fcyc = Vin/(4*R*C*|Vthr|)

This formula shows that the following variables are key to the basic accuracy of the oscillator: Vin, R, C, and 2*|Vthr| = (Vu - VL).

Vin, R and C accuracy: Given that Vin, R, and C do not drift unacceptably with temperature, their product can be trimmed with a trimmer R. Expected accuracy is 100 parts per million or +/-0.01% per degree C. However, wherever Vin comes from must be accurate. This is not foreordained. Observe that Vin actually has two components +Vin and -Vin. Call these Va and Vb and suppose that they are different by a factor k and an offset Ve:

- Va = +Vin, Vb = -(k*Vin + Veos); k is a factor such as 1.02. So we will want k = 1+e

- Tcyc = (0 - VL)*(R*C)/(+Vin) + (VL - 0)*(R*C)/(-Vin) + (0 - Vu)*(R*C)/(-Vin) + (Vu - 0)*(R*C)/(+Vin) =

- Tcyc = -(|VL|*R*C)/Va + (|VL|*R*C)/|Vb| -(Vu*R*C)/|Vb| + (Vu*R*C)/Va

- Tcyc = (R*C)*[ |VL|/Va + |VL|/|Vb| + Vu/|Vb| + Vu/Va ] = (R*C)*[ (|VL| + Vu)*(1/Va + 1/|Vb|) = (R*C)*[ (|VL| + Vu)*(1/Vin + 1/(k*Vin + Ve))

- Fcyc = 1/Tcyc = (|VL|+Vu)/(R*C)*[(Vin + (Vin*e + Veos))/(2 + (Veos/Vin + e)]

This rightmost term shows that Vin/2 is the result if all the errors are 0. If they are not, then the error contributed by e and Veos messes up the frequency Fcyc, but in a manner not obvious. Suppose Vin = 1, e = 0.01, Veos = -.01. The numerator has no error in it, but Vos/Vin

Vu and VL accuracy: Observe that the difference of Vu and VL is the variable. This means that if both Vu and VL have a common offset error e.g. Vos, then Vos cancels out:

- 2*|Vthr| = (Vu+Vos) - (VL+Vos) = (Vu - VL)

What we want is for |Vu| to equal |VL|. We can achieve 0.2% accuracy worst case with 0.1% resistors.

Operational amplifier and level-shifter

The problems the circuit must confront are:

- (1) Common mode noise (50-60 cycle noise on both signal leads)

- (2) Maximum input voltage Vin

- (3) Maximum common-mode voltage Vnoise + Vcm

- (4) Offset voltage errors Vos (an apparent voltage between the amplifier's V+ and V-; one wants this to be 0, but manufacturing variance and statistics rule out this possibility)

- (5) Shifting the DC level to 1.17 volts in order to place the DC trace in the center of the screen

- (6) No interaction between any gain adjustments and the DC level

Input Vin referenced to circuit common ("ground"):

Formula is the following:

- Vout = -Vm*R2/R1 + Vp*R4/R1*((R1+R2)/(R3+R4)) + Vr*R3/R1*((R1+R2)/(R3+R4)) + Vos*(R1+R2)/R1

- Where Vm is the voltage into the inverting-input resistor R1

- R2 is the feedback resistor

- Vp is the voltage into the non-inverting-input resistor R3

- R4 contects the op amp's + input to the reference Vr

- Vos is the offset voltage between the op amp's + and - inputs

This analysis assumes that there's a common "zero" reference point that Vm, Vp, Vr and Vout connect to.

To act as a differential amplifier with high common mode rejection we want:

- R3 = R1 and R2 = R4

So that the ratio R4/R1 = R2/R1, and (R1+R2)/(R3+R4) = 1, ideally. If this is the case then:

- Vout = (Vp - Vm)*R2/R1 + Vr + Vos*(R1+R2)/R1

In words: the gain for the voltage difference (Vp - Vm) is R2/R1, Vr is added to the output, and Vos is multiplied by the factor (R1+R2)/R1.

- Case when R2 >> R1: Vout ~= (Vp - Vm + Vos)*R2/R1 + Vr

- Case when R2 << R1: Vout ~= (Vp - Vm)*R2/R1 + Vr + Vos

In either case, the error-voltage Vos*R2/R1 or Vos alone is added to the output and thus can be corrected by adjusting Vr.

Detailed error analysis: This must be done with either a "Monte Carlo" analysis or a full-factorial analysis given the three worst cases (plus, minus, nominal) for each of 6 variables: R1, R2, R3, R4, Vr, Vos. This is 3^6 outcomes, not an unmanageable number.

- Example: Very worst case variance for a 4:1 attenuating probe: { R1 , R3 } each = { 20000 +0.1%, 20000, 20000 -0.1% } { R2, R4 } each = { 4990 +0.1%, 4990, 4990 -0.1% }, { Vr } = { 2.495 +1%, 0 ,2.495 -1% }, { Vos } = { +.002 , 0 , -0.002 }. More than likely the distribution will be predominately within 1/2 of these percentages, and if not the offenders can be culled (given adequate instrumentation). With a spreadsheet the MAX and MIN can be observed for a given Vin.

Input Vin truly floating, thus not referenced to circuit common ("ground"):

This occurs when Vin is a truly floating load -- a battery, a well-isolated DC supply, a coil of wire. The common-mode voltage should simply disappear, or if out of balance (e.g. because no twisted pair was used to connect Vin to the amplfier) just add to the signal. Thus, the formula is different:

- Vout = (Vin + Vos)*(R2+R4)/(R1 + R3) + Vr + Vos

In theory this formula allows one to eliminate two resistors -- R3 and R4 into the V+ input of the op amp. However, such a decision weakens the design in the following ways: (i) For the lowest input offset drift, input bias currents should be balanced, (ii) The input should be protected with a resistor.